flipflop - Turn a positive clock edge into a negative pulse to make a 74LS170/670 register file synchronous - Electrical Engineering Stack Exchange

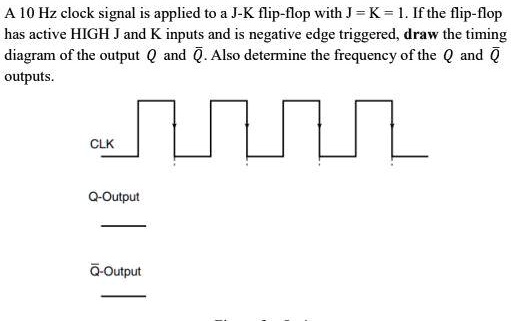

SOLVED: A 10 Hz clock signal is applied to a J-K flip flop with J = K = 0. If the flip-flop has active HIGH J and K inputs and is negative

flipflop - Turn a positive clock edge into a negative pulse to make a 74LS170/670 register file synchronous - Electrical Engineering Stack Exchange

2: Active level gating with clock-edge interrupt latency of 9 to 40 µs. | Download Scientific Diagram